Home /

Expert Answers /

Computer Science /

using-a-multicycle-cpu-where-each-stage-of-an-instruction-requires-1-clock-cycle-with-the-llowing-pa157

(Solved): Using a multicycle CPU where each stage of an instruction requires 1 clock cycle, with the llowing ...

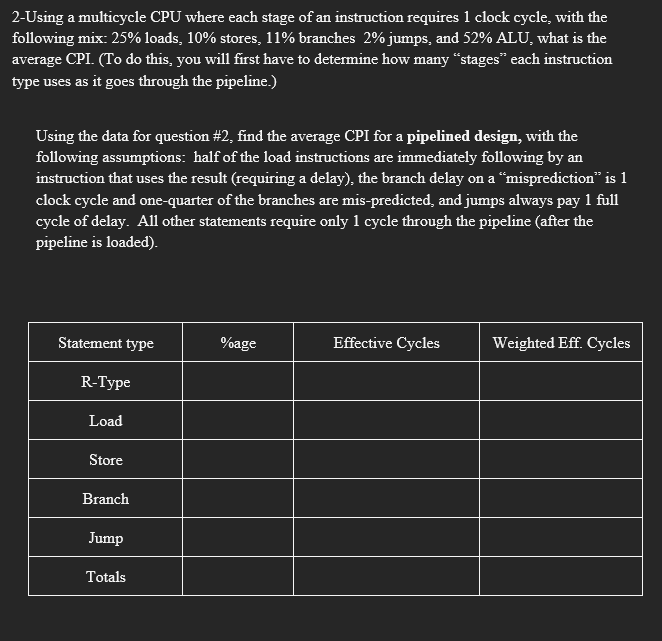

Using a multicycle CPU where each stage of an instruction requires 1 clock cycle, with the llowing mix: \( 25 \% \) loads, \( 10 \% \) stores, \( 11 \% \) branches \( 2 \% \) jumps, and \( 52 \% \) ALU, what is the verage CPI (To do this, you will first have to determine how many "stages" each instruction pe uses as it goes through the pipeline.) Using the data for question \#2, find the average CPI for a pipelined design, with the following assumptions: half of the load instructions are immediately following by an instruction that uses the result (requiring a delay), the branch delay on a "misprediction" is 1 clock cycle and one-quarter of the branches are mis-predicted, and jumps always pay 1 full cycle of delay. All other statements require only 1 cycle through the pipeline (after the pipeline is loaded).

Expert Answer

Solution :-) (2) Multicyle cpu requires 1 clock. A single Machine takes. 200+ 50 + 100 + 200 + 50 =