(Solved): 5. For the following set of instructions, indicate how many clock cycles would be used to execute t ...

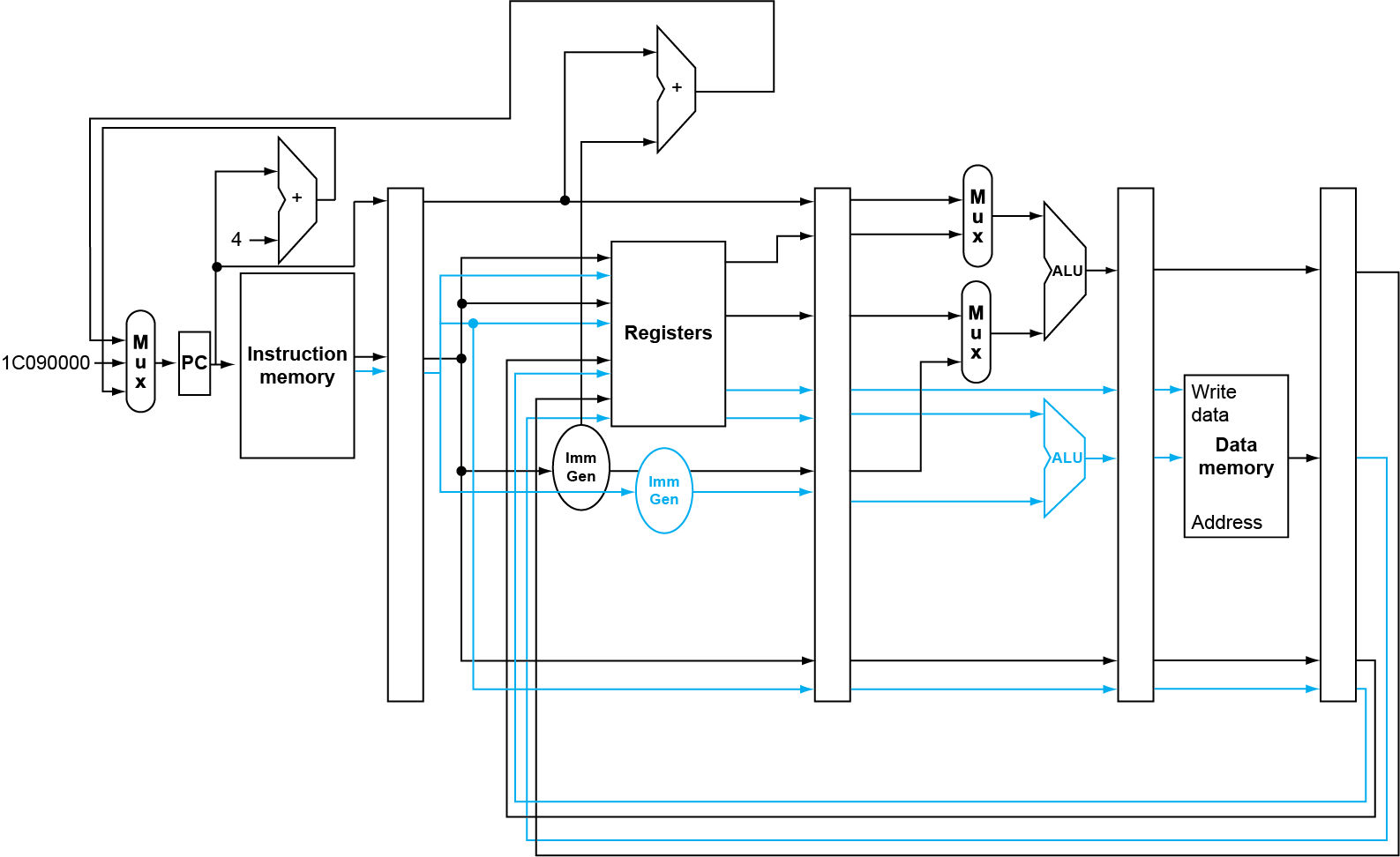

5. For the following set of instructions, indicate how many clock cycles would be used to execute those instructions by a CPU using a standard RISC-V datapath that implements forwarding as well as how many clock cycles would be used by a static dual-issue datapath (pictured below) that can execute one ALU/Branch and one Load/Store instruction per clock cycle. Show the scheduling for each CPU and mark any clock cycles where the pipeline is stalled as having no operation (NOP). You may reorder instructions to remove hazards.

slli x30, x15, 3

add x30, x11, x30

ld x20, 0(x30)

add x20, x20, x10

sd x20, 0(x30)

ld x21, 8(x30)

add x21, x21, x10

sd x21, 8(x30)

slli x31, x16, 3

add x31, x11, x31

ld x22, 0(x31)

sub x22, x22, x10

sd x22, 0(x31)

ld x23, 8(x31)

sub x23, x23, x10

sd x23, 8(x31)

or x28, x20, x22

or x29, x21, x23

and x12, x28, x29

6. Assume that you are working with the following direct mapped cache that is in the following initial state. All addresses for this problem should be treated as 16-bit addresses.

| Index | V | Tag | Data |

| 000 | 1 | 1000100101110 | Mem[1000 1001 0111 0000] |

| 001 | 0 | 0110100010111 | Mem[1100 1001 1110 1110] |

| 010 | 1 | 1010000110111 | Mem[1010 0001 1011 1010] |

| 011 | 1 | 0011110101110 | Mem[0011 1101 0111 0011] |

| 100 | 0 | 1100111000110 | Mem[1111 0001 1001 1100] |

| 101 | 0 | 0100111011000 | Mem[0110 1101 1000 0011] |

| 110 | 1 | 1110100000110 | Mem[1110 1000 0011 0110] |

| 111 | 1 | 0011110010011 | Mem[0011 1100 1001 1111] |

For each of the memory access requests below, specify the index and tag generated for the memory address as well as whether the request results in a cache hit or a cache miss.

A) 4140210

B) 2016510

C) 4895110

D) 3518410

E) 4389310

F) 267410

G) 5944610

H) 5944810

7. Draw a table representation of the state of the cache presented in problem 6 after processing memory requests A – H described in the problem above. Your table should include columns for index, valid bit, tag, and data. The data column contents can be described in terms of the memory location stored by that cache block (as opposed the actual contents of that memory).