(Solved): a) Consider a DRAM based on 1-Transistor DRAM cell and operating at \( \mathrm{V}_{\mathrm{OD}}=2.5 ...

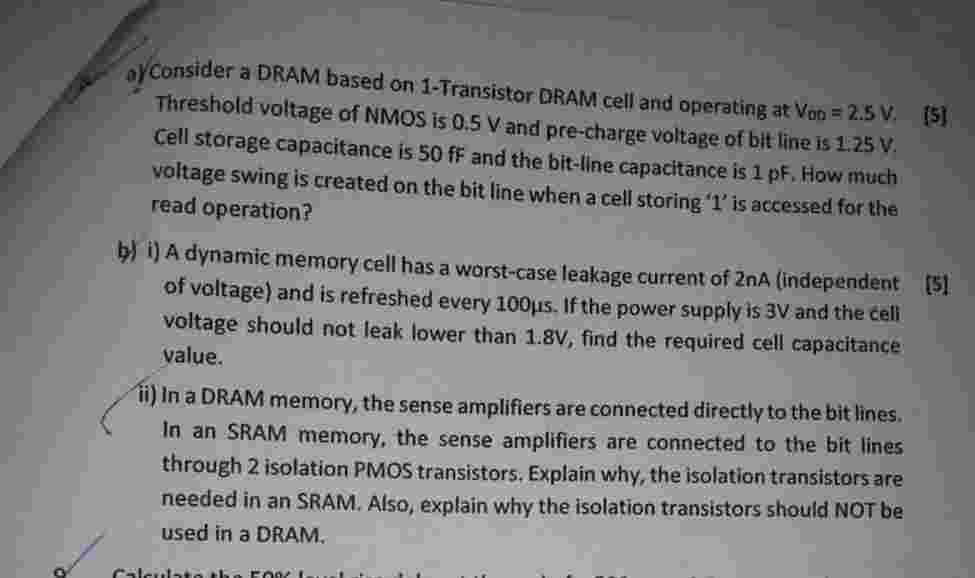

a) Consider a DRAM based on 1-Transistor DRAM cell and operating at \( \mathrm{V}_{\mathrm{OD}}=2.5 \mathrm{~V} \). Threshold voltage of NMOS is 0.5 V and pre-charge voltage of bit line is 1.25 V . Cell storage capacitance is 50 fF and the bit-line capacitance is 1 pF . How much voltage swing is created on the bit line when a cell storing ' 1 ' is accessed for the read operation? b) i) A dynamic memory cell has a worst-case leakage current of 2 nA (independent of voltage) and is refreshed every \( 100 \mu 5 \). If the power supply is 3 V and the cell voltage should not leak lower than 1.8 V , find the required cell capacitance value. ii) In a DRAM memory, the sense amplifiers are connected directly to the bit lines. In an SRAM memory, the sense amplifiers are connected to the bit lines through 2 isolation PMOS transistors. Explain why, the isolation transistors are needed in an SRAM. Also, explain why the isolation transistors should NOT be used in a DRAM.