Home /

Expert Answers /

Electrical Engineering /

consider-a-processor-with-32-bit-virtual-addresses-assuming-a-4-mathrm-kb-2-12-pa507

(Solved): Consider a processor with 32 -bit virtual addresses. Assuming a \( 4 \mathrm{~KB} \) ( \( 2^{12} \ ...

Consider a processor with 32 -bit virtual addresses. Assuming a \( 4 \mathrm{~KB} \) ( \( 2^{12} \) bytes) page size, 2 byte page table entries (which include one valid bit and one dirty bit), answer the

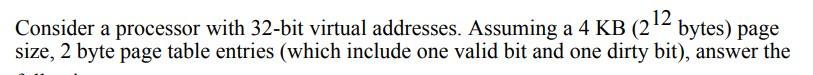

(d) [14pt] Consider a fully associative TLB with 4 virtual-to-physical page translation entries and the Least-Recently Used (LRU) method is used for the replacement strategy. The initial state of TLB is given in the first table. The initial state of page table is shown in the next page. If pages must be brought in from disk, increment the largest current page number in the table. For example, the next page fetched for the initial page table would be \( 0 x D \). We have following memory accesses \( 0 \times 00001300,0 \times 00002000 \) Please update the TLB entry for each memory access by filling out the following TLB state tables. Please use hexadecimal numbers for VPN and PPN. Use "I" for valid and "0" for invalid. Initial TI \( \mathrm{R} \) state TLB state after the \( 4^{\text {th }} \) access' TLB state after the \( 1^{\text {st }} \) access: TLB state after the \( 5^{\text {th }} \) access: TLB state after the \( 2^{\text {nd }} \) access: TLB state after the \( 6^{\text {th }} \) access: TLB state after the \( 3^{\text {rd }} \) access: TLB state after the \( 7^{\text {th }} \) access:

Expert Answer

I have provided the ans In Images

![(d) [14pt] Consider a fully associative TLB with 4 virtual-to-physical page translation entries and the Least-Recently Used (](https://media.cheggcdn.com/media/d30/d30c457c-5539-4acf-b0f1-10d6f89291b8/phplJ60vB)