(Solved): Consider the following Instructions whose pipeline execution components are represented in the table ...

Consider the following Instructions whose pipeline execution components are represented in the table below.

|

Instruction class |

Fetch (ps) |

Register Load (ps) |

ALU operation (ps) |

Data Access (ps) |

Register write (ps) |

Total Time (ps) |

|

Load word (lw) |

200 |

100 |

200 |

200 |

100 |

800 |

|

Store word (sw) |

200 |

100 |

200 |

200 |

100 |

700 |

|

R-format (add, sub, AND, OR, slt) |

200 |

100 |

200 |

100 |

600 |

|

|

Branch (beq) |

200 |

100 |

200 |

500 |

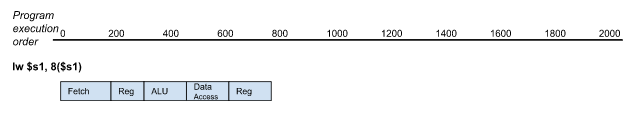

For the following instructions, map out the pipelined instruction execution timeline.

For a pipeline executed whose stages and timing are shown above, map out each stage of the pipelined instructions below. See the above as an example of how to map out the lw instruction. Assume there are no pipeline stalls or data hazards.

lw $t1, 4($s0)

add $t1, $t1, $s1

sw $s0, 8($t1)

b) Using part A for the pipeline execution time of the 3 instructions, what is the performance improvement (speed-up) seen with pipelining over the non-pipelined execution. Show and explain how you arrived at the speed-up.

Expert Answer

Consider the following Instructions whose pipeline execution components are renresented in the table below. For the following instructions, ma