Home /

Expert Answers /

Electrical Engineering /

in-the-figure-assume-all-switches-and-capacitors-are-ideal-that-is-the-switches-have-0-resistance-pa373

(Solved): In the figure, assume all switches and capacitors are ideal that is the switches have 0 resistance ...

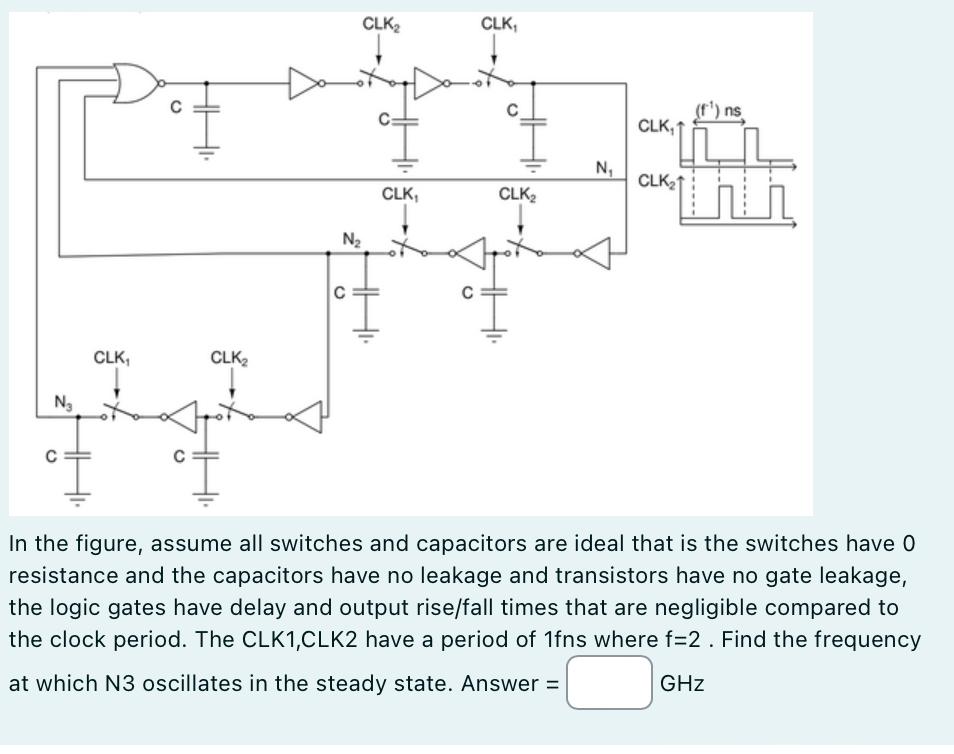

In the figure, assume all switches and capacitors are ideal that is the switches have 0 resistance and the capacitors have no leakage and transistors have no gate leakage, the logic gates have delay and output rise/fall times that are negligible compared to the clock period. The CLK1,CLK2 have a period of 1fns where

f=2. Find the frequency at which N3 oscillates in the steady state. Answer

=GHz