Home /

Expert Answers /

Electrical Engineering /

problem-1-12-pts-single-and-multiple-cycle-risc-v-microarchitecture-timing-consider-the-delays-g-pa280

(Solved): Problem 1 (12 pts) Single and multiple cycle RISC-V microarchitecture timing Consider the delays g ...

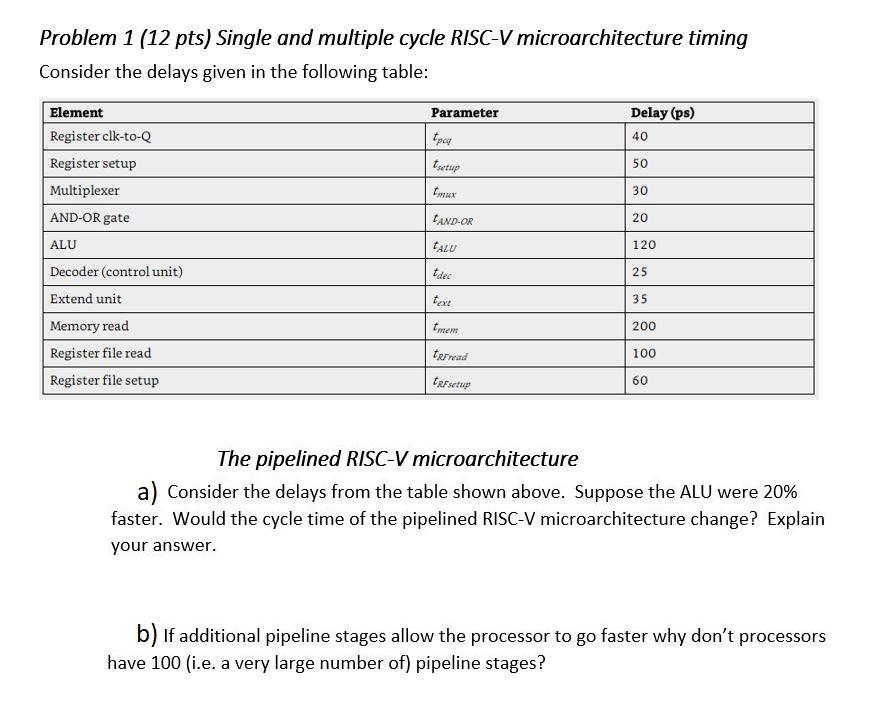

Problem 1 (12 pts) Single and multiple cycle RISC-V microarchitecture timing Consider the delays given in the following table: Element Parameter Delay (ps) Register clk-to-Q tpca 40 Register setup tsetup 50 Multiplexer tmux 30 AND-OR gate LAND-OR 20 ALU TALU 120 Decoder (control unit) tdec 25 Extend unit text 35 Memory read tmem 200 Register file read tFread 100 Register file setup tRFsetup 60 The pipelined RISC-V microarchitecture a) Consider the delays from the table shown above. Suppose the ALU were 20% faster. Would the cycle time of the pipelined RISC-V microarchitecture change? Explain your answer. b) If additional pipeline stages allow the processor to go faster why don't processors have 100 (i.e. a very large number of) pipeline stages?

Expert Answer

a) So to compute the clock cycle we need to take worst case time that any Intstuction will