(Solved): Write a behavioral VHDL module that implements the 8-bit shift register of Figure A. (a) Block diag ...

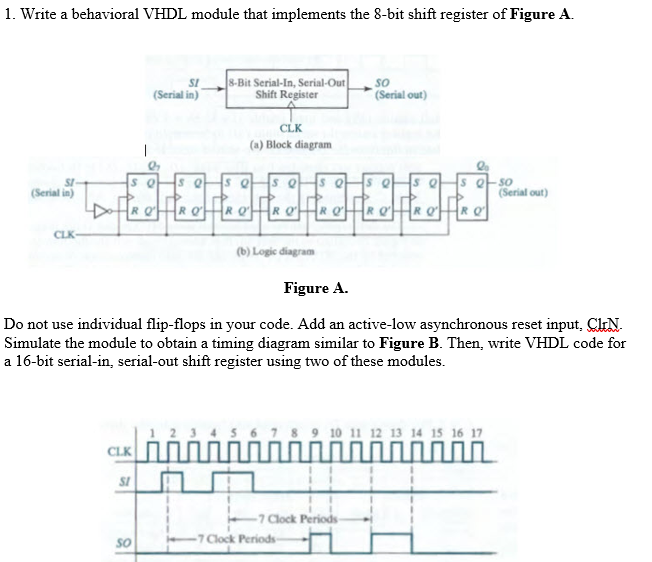

Write a behavioral VHDL module that implements the 8-bit shift register of Figure

A. (a) Block diagram (b) Logic diagram Figure A. Do not use individual flip-flops in your code. Add an active-low asynchronous reset input, ClrN. Simulate the module to obtain a timing diagram similar to Figure B. Then, write VHDL code for a 16-bit serial-in, serial-out shift register using two of these modules.